# 4165 ANYTHING I/O MANUAL

This page intentionally not blank

\_

# **Table of Contents**

| GENE  | RAL                                                                                                                                                                                                                                                                             | 1                        |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|       | DESCRIPTION                                                                                                                                                                                                                                                                     | 1                        |

| HARD' | WARE CONFIGURATION                                                                                                                                                                                                                                                              | 2                        |

|       | GENERAL MULTIPLEXED/NON-MULTIPLEXED MODE PC/104-PLUS SLOT NUMBER PULLUP ENABLE EEPROM ENABLE CONNECTOR POWER                                                                                                                                                                    | 2 2 3 3                  |

| CONN  | IECTORS                                                                                                                                                                                                                                                                         | 4                        |

|       | CONNECTOR LOCATIONS AND DEFAULT JUMPER POSITIONS I/O CONNECTOR PIN-OUT                                                                                                                                                                                                          | 5                        |

| OPER. | ATION                                                                                                                                                                                                                                                                           | 8                        |

|       | FPGA         FPGA PINOUT         MEMORY AND I/O REGIONS         CONFIGURATION         SC4I65       1         SC9030W       1         CLOCK SIGNALS       1         LEDS       1         PULLUP RESISTORS       1         I/O LEVELS       1         STARTUP I/O VOLTAGE       1 | 8<br>9<br>10<br>11<br>11 |

| SUPPI | LIED CONFIGURATIONS 1                                                                                                                                                                                                                                                           | 2                        |

|       | IOPR12 — 12 BIT WORD ACCESSED I/O PORT1IOPR24 — 24 BIT LONGWORD ACCESSED I/O PORT14I65LOOP — LOOPBACK TEST1HOST BASED MOTOR CONTROLLER1SOFTDMC MOTOR CONTROLLER1                                                                                                                | 2                        |

|       | RENCE<br>SPECIFICATIONS                                                                                                                                                                                                                                                         | 14                       |

### **GENERAL**

#### **DESCRIPTION**

The MESA 4I65 is a general purpose programmable I/O card for the PC/104-PLUS bus. The 4I65 uses a 200K gate Xilinx FPGA for all logic, so it is truly an "Anything I/O" card. The FPGA is downloadable from the PC/104-PLUS bus side, allowing creation of almost any kind of specialized I/O function, even including micro-controllers in the FPGA.

Several pre-made functions are provided, including a 72 bit parallel I/O card with three 24 bit ports a 12 channel host based servo motor controller, a 8 channel microcontroller based servo motor controller (*Soft*DMC), and a 8 channel, 32 bit timer counter card capable of running at 100 MHz. VHDL source is provided for all examples.

All I/O bits are 5V tolerant and can sink 24 mA. Pullup resistors are provided for all pins so that they may be connected directly to opto-isolators, contacts etc.

The 4l65 uses three 50 pin connectors with I/O module rack compatible pinouts and interleaved grounds.

### HARDWARE CONFIGURATION

#### **GENERAL**

Hardware setup jumper positions assume that the 4I65 card is oriented in an upright position, that is, with the PC/104-PLUS connector on the top and the white PCB markings right side up.

#### MULTIPLEXED/NON MULTIPLEXED MODE

The local bus interface from the PCI bridge chip to the FPGA can operate in two modes. Multiplexed and Non-multiplexed. In multiplexed mode the local bus addresses are presented on the data lines at the beginning of the local bus cycle. In non-multiplexed mode, the addresses are presented on separate local bus address pins. The multiplexed mode has the advantage that all 32 address bits are available to the FPGA chip. The disadvantage is that the FPGA configuration must latch the addresses. The Multiplexed mode is the default, and all of the provided FPGA configurations assume that the multiplexed mode is used.

| W4   | MODE                  |

|------|-----------------------|

| UP   | MULTIPLEXED (DEFAULT) |

| DOWN | NON-MULTPLEXED        |

#### PC/104-PLUS SLOT NUMBER

PC104-PLUS cards have a slot number setting that cooresponds to the physical PCI slots on standard PCI systems. No two I/O cards in a PC104-PLUS stack can have the same slot number. The slot numbers are assigned with jumpers W2 and W3. The following table shows 4I65 slot numbers:

| W2   | W3   | SLOT |

|------|------|------|

| DOWN | DOWN | 0    |

| DOWN | UP   | 1    |

| UP   | DOWN | 2    |

| UP   | UP   | 3    |

# HARDWARE CONFIGURATION

#### **PULLUP ENABLE**

The Xilinx FPGA on the 4l65 has the option of having weak pullups on all I/O pins at power up or reset. This may be desirable if the 4l65 is used without its 3.3k pullups on I/O pins. To enable the built-in pullups, jumper W8 should be placed in the right position. This is the default position and W8 must be in this position on first revision (no Rev. letter) 4l65 cards. To disable the internal pullups, W8 should be in the left position.

#### **EEPROM ENABLE**

The PLX9030 PCI-Local bus bridge chip is configured at power up via a serial EEPROM. If the EEPROM is somehow mis-programmed or corrupted, it can be impossible to re-write the EEPROM from the PC/104-PLUS bus. To avoid this problem, The EEPROM can be temporarily disabled. W5 controls the EEPROM enable function, When W5 is in the up position (default) the EEPROM is enabled. When W5 is in the down position, the EEPROM is disabled.

#### **CONNECTOR POWER**

The power connection on the I/O connectors can supply either 3.3V or 5V power. Supplied power should be limited to 400 mA total.

W7 selects the power supplied to P1. (The right hand I/O connector) When W7 is in the up position, 5V power is supplied to P1. When W7 is in the down position, 3.3v power is supplied to P1.

W1 selects the power supplied to P3. (The left hand I/O connector) When W1 is in the left position, 5V power is supplied to P3. When W1 is in the right position, 3.3v power is supplied to P3.

W6 selects the power supplied to P4. When W6 is in the up position, 5V power is supplied to P4. When W6 is in the down position, 3.3v power is supplied to P4.

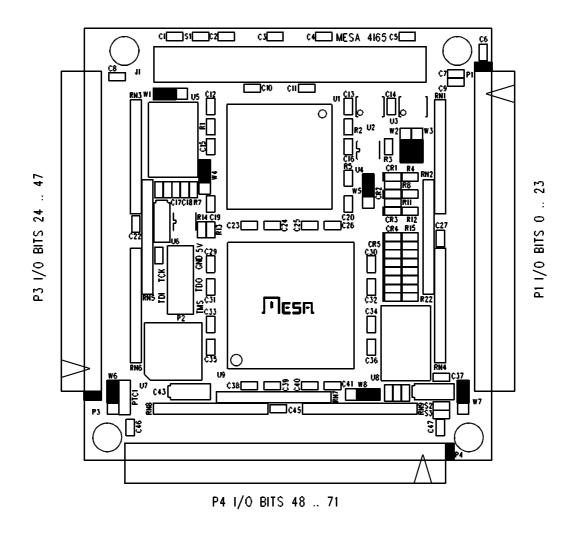

# **CONNECTOR LOCATIONS AND DEFAULT JUMPER POSITIONS**

### I/O CONNECTORS

P1, P3, and P4 are the 4I65s I/O connectors. These are 50 pin box headers that mate with standard 50 conductor female IDC connectors. For information on which I/O pin connects to which FPGA pin, please see the 4I65IO.PIN file on the 4I65 distribution disk. 4I65 IO connector pinouts are as follows:

#### **P1 CONNECTOR PINOUT**

| PIN | FUNC  | PIN | FUNC | PIN | FUNC | PIN | FUNC |

|-----|-------|-----|------|-----|------|-----|------|

| 1   | IO0   | 2   | GND  | 3   | IO1  | 4   | GND  |

| 5   | IO2   | 6   | GND  | 7   | IO3  | 8   | GND  |

| 9   | IO4   | 10  | GND  | 11  | IO5  | 12  | GND  |

| 13  | IO6   | 14  | GND  | 15  | IO7  | 16  | GND  |

| 17  | IO8   | 18  | GND  | 19  | IO9  | 20  | GND  |

| 21  | IO10  | 22  | GND  | 23  | IO11 | 24  | GND  |

| 25  | IO12  | 26  | GND  | 27  | IO13 | 28  | GND  |

| 29  | IO14  | 30  | GND  | 31  | IO15 | 32  | GND  |

| 33  | IO16  | 34  | GND  | 35  | IO17 | 36  | GND  |

| 37  | IO18  | 38  | GND  | 39  | IO19 | 40  | GND  |

| 41  | IO20  | 42  | GND  | 43  | IO21 | 44  | GND  |

| 45  | IO22  | 46  | GND  | 47  | IO23 | 48  | GND  |

| 49  | POWER | 50  | GND  |     |      |     |      |

# I/O CONNECTORS

# **P3 CONNECTOR PINOUT**

| PIN | FUNC  | PIN | FUNC | PIN | FUNC | PIN | FUNC |

|-----|-------|-----|------|-----|------|-----|------|

| 1   | IO24  | 2   | GND  | 3   | IO25 | 4   | GND  |

| 5   | IO26  | 6   | GND  | 7   | IO27 | 8   | GND  |

| 9   | IO28  | 10  | GND  | 11  | IO29 | 12  | GND  |

| 13  | IO30  | 14  | GND  | 15  | IO31 | 16  | GND  |

| 17  | IO32  | 18  | GND  | 19  | IO33 | 20  | GND  |

| 21  | IO34  | 22  | GND  | 23  | IO35 | 24  | GND  |

| 25  | IO36  | 26  | GND  | 27  | IO37 | 28  | GND  |

| 29  | IO38  | 30  | GND  | 31  | IO39 | 32  | GND  |

| 33  | IO40  | 34  | GND  | 35  | IO41 | 36  | GND  |

| 37  | IO42  | 38  | GND  | 39  | IO43 | 40  | GND  |

| 41  | IO44  | 42  | GND  | 43  | IO45 | 44  | GND  |

| 45  | IO46  | 46  | GND  | 47  | IO47 | 48  | GND  |

| 49  | POWER | 50  | GND  |     |      |     |      |

#### I/O CONNECTORS

#### **P4 CONNECTOR PINOUT**

| PIN | FUNC  | PIN | FUNC | PIN | FUNC | PIN | FUNC |

|-----|-------|-----|------|-----|------|-----|------|

| 1   | IO48  | 2   | GND  | 3   | IO49 | 4   | GND  |

| 5   | IO50  | 6   | GND  | 7   | IO51 | 8   | GND  |

| 9   | IO52  | 10  | GND  | 11  | IO53 | 12  | GND  |

| 13  | IO54  | 14  | GND  | 15  | IO55 | 16  | GND  |

| 17  | IO56  | 18  | GND  | 19  | IO57 | 20  | GND  |

| 21  | IO58  | 22  | GND  | 23  | IO59 | 24  | GND  |

| 25  | IO60  | 26  | GND  | 27  | IO61 | 28  | GND  |

| 29  | IO62  | 30  | GND  | 31  | IO63 | 32  | GND  |

| 33  | IO64  | 34  | GND  | 35  | IO65 | 36  | GND  |

| 37  | IO66  | 38  | GND  | 39  | IO67 | 40  | GND  |

| 41  | IO68  | 42  | GND  | 43  | IO69 | 44  | GND  |

| 45  | IO70  | 46  | GND  | 47  | IO71 | 48  | GND  |

| 49  | POWER | 50  | GND  |     |      |     |      |

#### **4I65 JTAG CONNECTOR**

P2 is a JTAG programming connector. It is not normally used since the 4l65 can be programmed via the PC/104-PLUS interface, but can be useful when debugging. Note that the /PROGRAM pin must be de-asserted to be able to use the JTAG interface.

#### **P2 CONNECTOR PINOUT**

| PIN | FUNC | PIN | FUNC | PIN | FUNC |

|-----|------|-----|------|-----|------|

| 1   | TMS  | 2   | TDI  | 3   | TDO  |

| 4   | TCK  | 5   | GND  | 6   | +5V  |

#### **FPGA**

The 4l65 use a Xilinx Spartan-II 200k gate FPGA in a 208 pin QFP package: XC2S200-PQ208

#### **FPGA PINOUT**

The local bus and I/O interface FPGA pinouts are described in the 4I65INFC.PIN and 4I65IO.PIN files in CONFIGS directory of the distribution disk. The 4I65IO.PIN file may be used as a template for custom configurations

#### **MEMORY AND I/O REGIONS**

The PLX9030 maps 6 different IO/memory regions into host address space. Two of these address spaces are for PLX9030 configuration register access.

#### **PLX9030 CONFIGURATION REGISTERS**

| BUS SPACE   | MEM - I/O | WIDTH   | RANGE     |

|-------------|-----------|---------|-----------|

| BUS SPACE 0 | MEMORY    | 32 BITS | 128 BYTES |

| BUS SPACE 1 | I/O       | 32 BITS | 128 BYTES |

The PLX9030 PCI bridge allows 4 separate memory or I/O regions to be mapped to the local bus that connects to the FPGA. The default EEPROM configuration sets these up as follows:

#### LOCAL BUS (FPGA) ACCESS AREA

| BUS SPACE   | MEM - I/O | WIDTH   | RANGE                 |

|-------------|-----------|---------|-----------------------|

| BUS SPACE 2 | I/O       | 16 BITS | 256 BYTES (128 WORDS) |

| BUS SPACE 3 | I/O       | 32 BITS | 256 BYTES (64 LONGS)  |

| BUS SPACE 4 | MEM       | 16 BITS | 64K BYTES (32K WORDS) |

| BUS SPACE 5 | MEM       | 32 BITS | 64K BYTES (16K LONGS) |

#### CONFIGURATION

Before the 4I65 can do anything useful it must have its FPGA configuration data downloaded from the host CPU to the FPGA on the 4I65. This is done by writing a series of bytes from the configuration file to the 4I65 card's configuration data register. Configuration data is written a byte at a time to any of the I/O or memory bus space regions mapped to the 4I65s local bus.

The FPGA configuration control bits must be manipulated before configuration data can be sent to the FPGA. These control bits are controlled via GPIO pins of the PLX9030 PCI bridge. The PLX9030s GPIO pins are connected to the following FPGA configuration pins:

| GPIO  | DIRECTION | FPGA       |

|-------|-----------|------------|

| GPIO3 | IN        | DONE       |

| GPIO4 | IN        | /INIT      |

| GPIO5 | OUT       | STATUS LED |

| GPIO7 | OUT       | /WRITE     |

| GPIO8 | OUT       | /PROGRAM   |

The GPIO pin functions and directions are setup by the EEPROM so need not normally be changed. Refer to the PLX 9030 manual if you need low level access to these control bits

#### **SC4I65**

A utility program SC4I65.EXE is provided to send configuration files to the 4I65. The Pascal and C source for this program is available on the distribution disk, and can be used as an example for writing a custom version of download software. SC4I65 is invoked with the FPGA configuration file and the 4I65 configuration base address on the command line:

SC4165 FPGAFILE.BIN

#### SC4165

SC4I65 uses binary FPGA configuration files. These files can be standard Xilinx BIT files or PROM format files. The SC4I65 utility sends PROM files directly to the 4I65. BIT files have their headers stripped and are bit reversed before being sent to the

#### **SC9030W**

Another utility SC9030W is provided for Windows 2000 and Windows XP This utility requires the PLX9030.SYS driver and PLXAPI.DLL API SHIM to work. The source for SC9030W can be used as an example of how to access the configured 4l65cards under Windows 2K or XP.

SC4I65 and SC9030W use binary FPGA configuration files. These files can be standard Xilinx BIT files or PROM format files. The utilities send PROM files directly to the 4I65. BIT files have their headers stripped and are bit reversed before being sent to the 4I65.

### **CLOCK SIGNALS**

The 4 FPGA clock signals on the 4I65 are routed to 4 separate clock sources. GCLK0 connects IO0, GCLK1 connects to IO48, GCLK2 connects to the local bus clock which is the same as the PCI clock, normally 33 MHz, and GCLK3 connects to a 50 MHz crystal oscillator on the 4I65 card.

#### **LEDS**

The 4l65 has 8 FPGA driven user LEDs, and 3 status LEDs. The user LEDs can be used for any purpose, and can be helpful as a simple debugging feature. A low output signal from the FPGA lights the LED. See the 4l65lO.PIN file for FPGA pin locations of the LED signals. The status LEDs reflect the state of the FPGA's DONE, /INIT, and the PCI bridge's GPIO5 bit.

#### **PULLUP RESISTORS**

All I/O pins are provided with pullup resistors to allow connection to open drain, open collector, or OPTO devices. These resistors are 10 pin, 9 resistor SIP networks. The resistor networks are socketed to allow the user to select different values. Pin 10 of all the resistor networks is grounded, allowing the use of 220/330 Ohm termination networks if desired on the receiving end of a high speed bus.

#### **IO LEVELS**

The Xilinx FPGAs used on the 4I65 have programmable I/O levels for interfacing with different logic families. The 4I65 does not support use of the I/O standards that require input reference voltages, so only 5 I/O options can be used. The available I/O options are LVTTL (5V tolerant), PCI33\_5 (5V tolerant), PCI33\_3, PCI66\_3, and LVCMOS2. Two of the I/O options allow 5V inputs.. I/O levels of the users I/O pins do not have to be +5V compatible if not needed, but it is suggested to use one of the 5V tolerant I/O standards to avoid possible damage if larger than 3.3V signals are applied to I/O pins.

Note that even though the 4I65s FPGA can tolerate 5V signal inputs, its outputs will not swing to 5V. The outputs are push pull CMOS outputs that will drive to the output supply rail of 3.3V. This is sufficient for TTL compatibility but may cause problems with some types of loads. For example when driving an LED that has its anode connected to 5V, the 3.3V high level may not completely turn the LED off. To avoid this problem, either drive loads that are ground referred, Use 3.3V as the VCC for VCC referred loads, or tristate the output signals when no drive is desired (open drain).

#### STARTUP I/O VOLTAGE

After power-up or system reset and before the the FPGA is configured, the pull-up resistors will pull all I/O signals to a high level. If the FPGA is used for motion control or controlling devices that could present a hazard when enabled, external circuitry should be designed so that this initial state results in a safe condition.

### SUPPLIED CONFIGURATIONS

#### IOPR12

The IOPR12 configuration creates a simple 72 bit parallel I/O port. IOPR12 is a word device, all accesses read or write 16 bit words. IOPR12 creates six 12 bit ports, 2 ports per I/O connector. Each I/O bit can be individually programmed to be input or output. All I/O bits will be input on startup. For information on the register map of the IOPR12 configuration, see the regmap file in the /configs/IOPR12 directory of the 4I65 distribution disk

#### IOPR24

The IOPR24 configuration creates a simple 72 bit parallel I/O port. IOPR24 is 32 bit device, all accesses read or write 16 bit words. IOPR24 creates three 24 bit ports, one port per I/O connector.. Each I/O bit can be individually programmed to be input or output. All I/O bits will be input on startup. For information on the register map of the IOPR24 configuration, see the regmap file in the /configs/IOPR24 directory of the 4I65 distribution disk.

#### 4165LOOP

The IOPR24 configuration provides a simple way to check that all the I/O pins are OK and that most of the host interface is working. A loopback program (4I65LOOP) is provided for doing this testing. 4I65LOOP depends on an external loopback cable between I/O connectors P2, P3, and P4. 4I65LOOP perform a rotating bit test with one I/O connector programmed as outputs and the other two as inputs. All combinations of inputs and outputs are tested. In addition, a 32 bit register readback test is performed to verify 32 bit local data bus functionality.

#### **HOSTMOT2**

The HOSTMOT2 configuration is a up to 12 channel host based servo or step motor motor controller. Host based controllers depend on the host CPU to "close" the servo loop. This has advantages and disadvantages. One advantage is that less hardware is needed, since host based software does all the math and handles all the control bits. Another advantage is that since the host based software is easily examined and modified, it is more amenable to customization and is more useful as a teaching tool. One disadvantage is that host based motor controllers depend on fast interrupt response time, since the control loop is an interrupt driven background task. This means that host based motor controllers don't tend to work well with multitasking operating systems such as Windows or Unix. They will work with real-time operating systems or simple operating systems like DOS.

# **SUPPLIED CONFIGURATIONS**

#### **HOSTMOT2**

HOSTMOT2 is available in several configurations the vary the number of servo or step generator channels, plus miscellaneous I/O options including 32 bit buffered UARTs, SPI interfaces, SSI interfaces etc.

Demonstration software provided with the 4l65 implements a PID + feedforward control loop, plus a ramp-up, slew, ramp-down, profile generator for position control applications. Demo program (newmove.exe) and sources are located in the /configs/hostmot2/support directory of the 4l65 distribution disk image.

# **SUPPLIED CONFIGURATIONS**

#### **SOFTDMC**

The *Soft*DMC configuration creates a 4 or 8 axis processor based servo motor controller, with the processor embedded in the FPGA. The *Soft*DMC configuration has the advantage that the embedded processor takes care of all time critical functions, so it can control motor position and motions without host intervention.

The *Soft*DMC configuration has programmable sample and PWM rates, and can operate 4 axis at up to 30 KHz sample rate and 8 axis at up to 15 KHz sample rate.

The control loop is a PID+F loop (F=feedforward) with 16 bit tuning parameters. Position and Velocity use 32 bit parameters for wide range.

The profile generator supports position, velocity, and homing modes. Position mode includes ramp-up, slew, ramp-down motions. Velocity mode supports breakpoints and a linked list parameter loading system for accurate profiling. Profile generator uses 48 bit accumulator to allow velocities down to ~2 turns per day (500 line - 2000 count encoder, 4 KHz sample rate)

There is a separate manual available for the SoftDMC motion controller.

Demo program softdemo.exe), and tuning program (newdmc.exe) and sources are located in the /configs/softdmc/support directory of the 4l65 distribution disk.

# **REFERENCE**

# **SPECIFICATIONS**

| POWER                         | MIN    | MAX     | NOTES:             |

|-------------------------------|--------|---------|--------------------|

| POWER SUPPLY                  | 4.5V   | 5.5V    |                    |

| POWER CONSUMPTION:            |        | 1000 mA | Depends on FPGA    |

|                               |        |         | Configuration      |

| MAX 5V CURRENT TO I/O CONNS   |        | 500 mA  | Total of all three |

| MAX 3.3V CURRENT TO I/O CONNS |        | 500 mA  | Total of all three |

|                               |        |         |                    |

| TEMPERATURE RANGE -C version  | 0 °C   | +70 °C  |                    |

| TEMPERATURE RANGE -I version  | -40 °C | +85 °C  |                    |